PCを自作したことがある人ならば、マザーボードには様々な部品があり、CPUの他にGPUやその他のチップセットが搭載されているのを見ることがあるだろう。

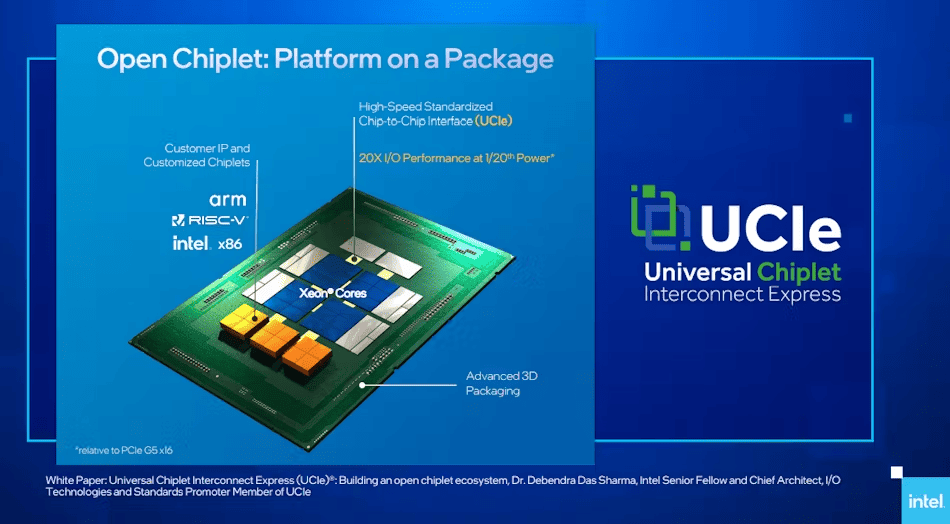

だが、半導体技術の進歩により、こうしたチップは今後は1つのチップレットになる可能性も示されている。それを実現するのが、システム・イン・パッケージ(SiP)における多機能チップレット間の接続を標準化する仕様であるUniversal Chiplet Interconnect Express(UCIe)だが、Intelの研究者らは、これに従って開発されたシステムの性能をさらに高めるための新たなビジョンについて『Nature Electronics』誌に掲載された論文において概説している。

「私たちは、PCI-Express、CXL、UCIeなど、多世代に渡る技術を推進してきました。UCIeの文脈では、UCIe 1.0を完成させた後、電力効率に優れた性能に対する飽くなき要求に応えるため、理想的には1ビット当たりの消費電力を1桁下げながら、もう1、2桁高い性能を実現する方法を検討してきました」と、Intelのシニアフェローであり、メモリ・I/O技術、データプラットフォーム、人工知能グループの共同GMであるDebendra Das Sharma博士はTech Xploreに語った。

シリコンとパッケージング技術の進歩により、回路基板内の個々のチップを接続するバンプの間隔(バンプピッチとも呼ばれる)を縮小する新たな可能性が開かれた。Das Sharma博士とその共同研究者による研究の主な目的は、オンパッケージ相互接続のバンプピッチが縮小され続ける中で、研究者がシステムの性能と電力効率をさらに高めることができる戦略を探ることだ。

「3Dを含む先端パッケージングのトレンドは、バンプピッチの縮小です。バンプピッチとは、2つのチップレットを接続する2つのバンプ間の最小距離のことです。つまり、バンプピッチが小さくなればなるほど、2つのチップレット間の配線が増えることになります。主に外部相互接続から生まれる自然な傾向は、周波数を高くすることだ。しかし、この場合、配線の数が増えるため、回路をフィットさせ、より低い電力を得るためには、周波数を低くする必要があります」と、Das Sharma博士は説明する。

研究の一環として、博士らは、パッケージ化されたチップレットをベースにしたシステムにおいて、周波数を下げることの効果をさらに探るための解析を行った。その結果、従来のチップ接続インターフェイスとは異なり、UCIe配列技術は、バンプ相互接続のピッチが小さくなるにつれて、周波数低減の恩恵を大きく受けることがわかった。

特に、周波数の低減は、システムの電力効率と全体的な性能の両方を向上させることが判明した。基礎となるアーキテクチャがさらに進化するにつれて、相互接続回路を持つシステムの将来の進歩に貢献しうる、新しい価値あるアプローチが明らかになったのだ。

「我々は、過去に業界標準仕様に影響を与えたのと同じように、標準化を通じて幅広い業界が我々の研究から恩恵を受けられることを願っています。個人的には、UCIe、CXL、PCIeのような業界標準の相互接続を進化させるために、20年以上取り組んできたように、今後も取り組んでいくつもりです。チップレットとUCIeの文脈では、旅は始まったばかりであり、この先のチャンスに興奮しています」と、Das Sharma博士は述べている。

論文

- Nature Electronics: High-performance, power-efficient three-dimensional system-in-package designs with universal chiplet interconnect express

参考文献

- TechXplorer: Intel introduces approach to boost power efficiency, reliability of packaged chiplet ecosystems

研究の要旨

Universal chiplet interconnect express (UCIe)は、複数のサプライヤーのチップレットをパッケージングできるチップレットエコシステムのためのオープンな業界標準インターコネクトです。UCIe 1.0仕様は、プレーナ型相互接続による標準および先進のパッケージング技術を使用した相互運用性を定義しています。ここでは、チップレットの 3 次元集積に向けたパッケージング技術の進歩に伴い、バンプ相互接続のピッチが縮小する中で、UCIe の発展について考察する。パッケージのバンプピッチが1μmまで連続する場合のダイ・ツー・ダイ・ソリューションを報告し、回路アーキテクチャの詳細と性能結果を示す。従来の信号インターフェイスに見られる傾向とは異なり、バンプピッチが小さくなるにつれて周波数を下げることで、これらのアーキテクチャで最も電力効率に優れた性能を達成できることを、我々の解析は示唆している。当社のアーキテクチャ・アプローチは、バンプ・ピッチが1µmに近づくにつれて、モノリシック・システム・オン・チップ設計に近づくか、それを上回る消費電力、性能、信頼性特性を提供します。

コメントを残す