3nm以下の微細化を実現するためのキーテクノロジーのひとつに、チップ裏面での電力供給がある。この新しいアプローチは、シグナル・インテグリティ(SI)を向上させ、配線混雑を緩和するが、同時に、今日、簡単な解決策がない新たな課題を生み出しており、実用化に向けた研究が進められている。

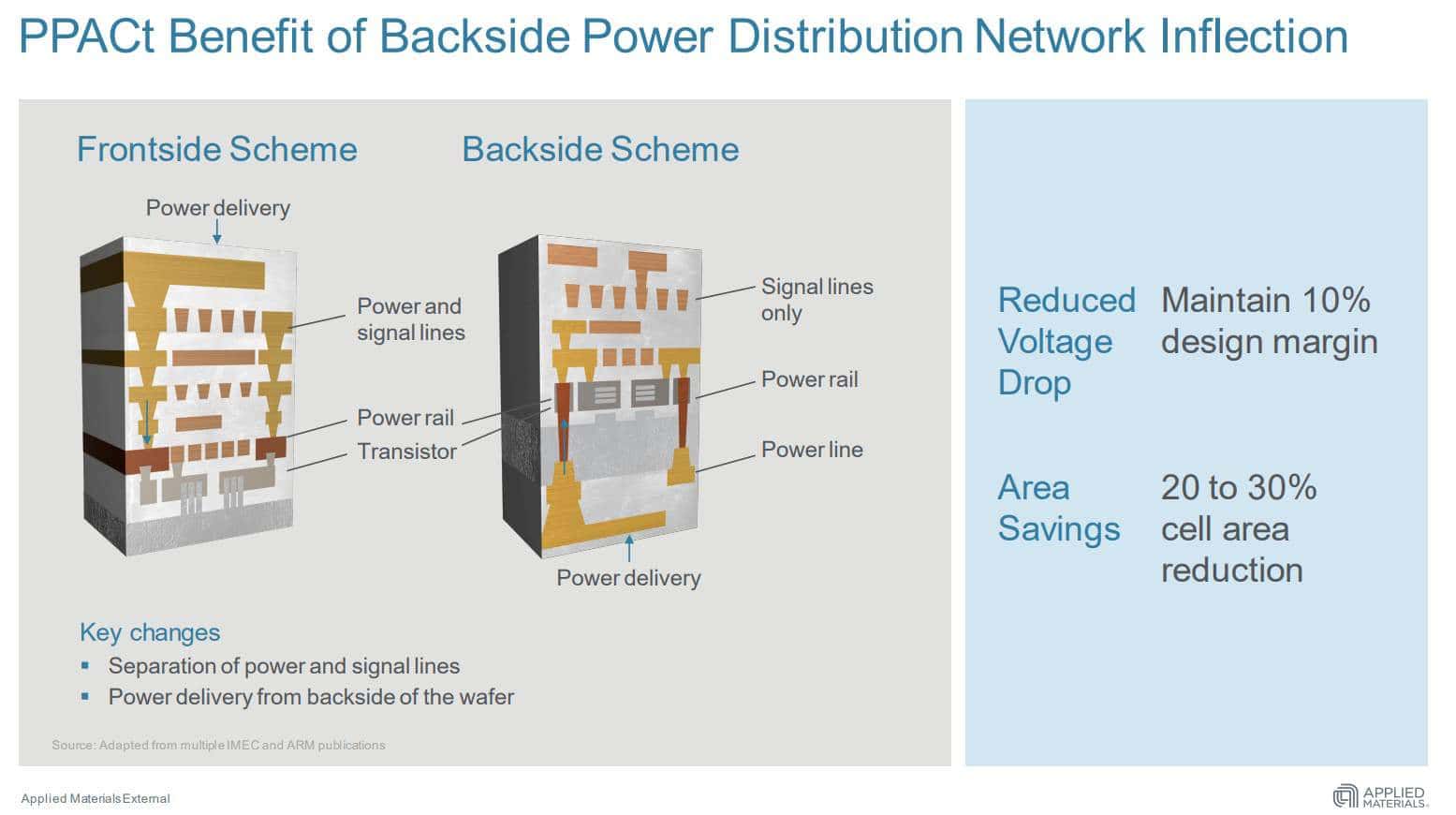

裏面電源供給網(Backside Power Delivery: BPD、BSP、またはBackside Power Delivery Network: BSPDN)は、ウェハーの表側と裏側でそれぞれ、信号と電力のやりとりを分離する物だ。これまでの電力供給はウェハーの表側でBEOL(Back End Of Line)プロセスにより製造された低抵抗の金属ワイヤのネットワークとして実現されてきた。この電力供給網(PDN)は、信号ネットワーク、すなわち信号を伝送するために設計された相互接続と空間を共有していた。だが、BSPDNによりこれが排除されることで、インターコネクトのスケーリングを推し進めることが出来る。また、メタルパターニングの複雑さが軽減されることで、コストの削減も可能になるのだ。Intel、Samsung、TSMCの3社はいずれも、2nmノード近辺で何らかの形でBSPDNを実装する計画を発表している。

目次

BSPDNはなぜ必要なのか?

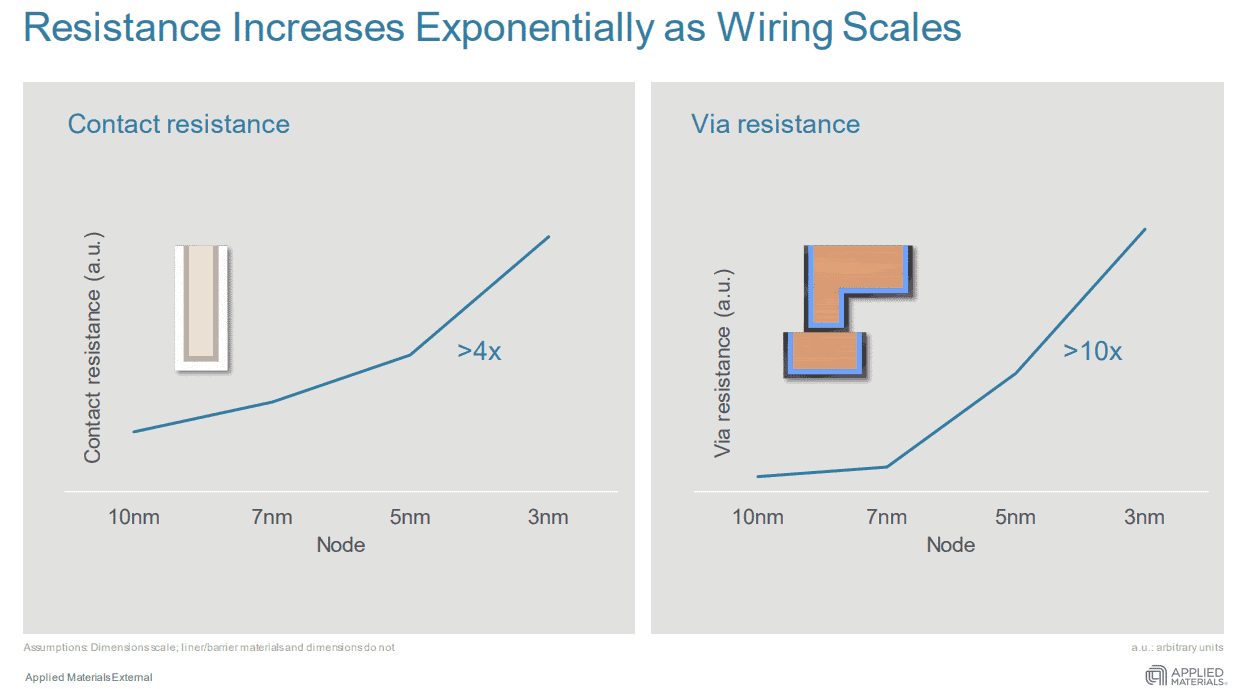

BSPDNは、トランジスタの微細化における大きな問題の一つであるエネルギーの問題を解決しようとしたものだ。具体的には、電力の供給に伴う抵抗の問題である。抵抗とは、材料が電流にどれだけ強く抵抗するかを示す特性であることは、おそらく学生時代に授業のどこかで聞いたことがあるかもしれない。銅のような材料は電気抵抗が低いことが知られているが、その銅線もサイズを小さくしていくと、抵抗は指数関数的に上昇し始めるのだ。

その中間的な解決策として、コバルトなどの新しい金属層が登場した。コバルトは、トランジスタに信号と電力を送るために必要な電荷をワイヤに保持させるのに役立っていたが、それも限界に達しつつあり、これがトランジスタ微細化の妨げになっている。

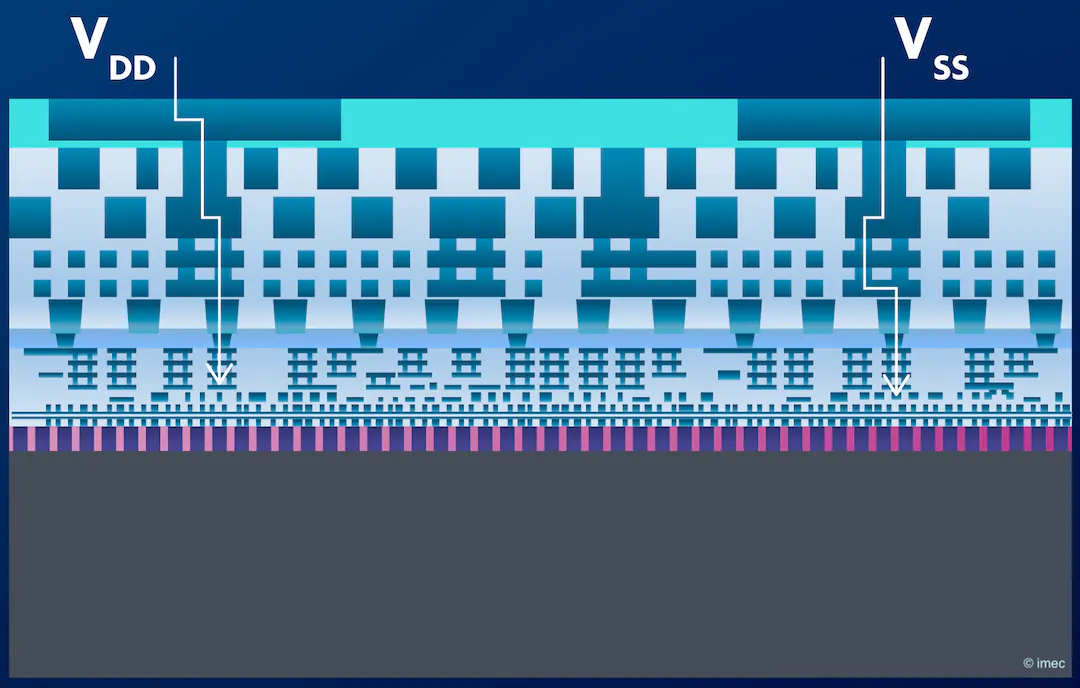

パッケージからトランジスタに電力を供給するために、電子はBEOLスタックの15~20層すべてを、トランジスタに近づくほど狭くなる(つまり抵抗が大きくなる)金属ワイヤとViaを通って横断する。その際、電子はエネルギーを失い、電力供給が滞ったり、電力を下げるとIR(抵抗)が低下したりする。トランジスタの近く、つまりスタンダードセルレベルに到達すると、電子は BEOLのMINT層に構成された VDD と VSS の電源およびグランドレールに到達する。これらのレールは、各スタンダードセルの境界と間にスペースを取る。ここから、ミドル・オブ・ライン配線網を通じて、各トランジスタのソースとドレインに接続される。

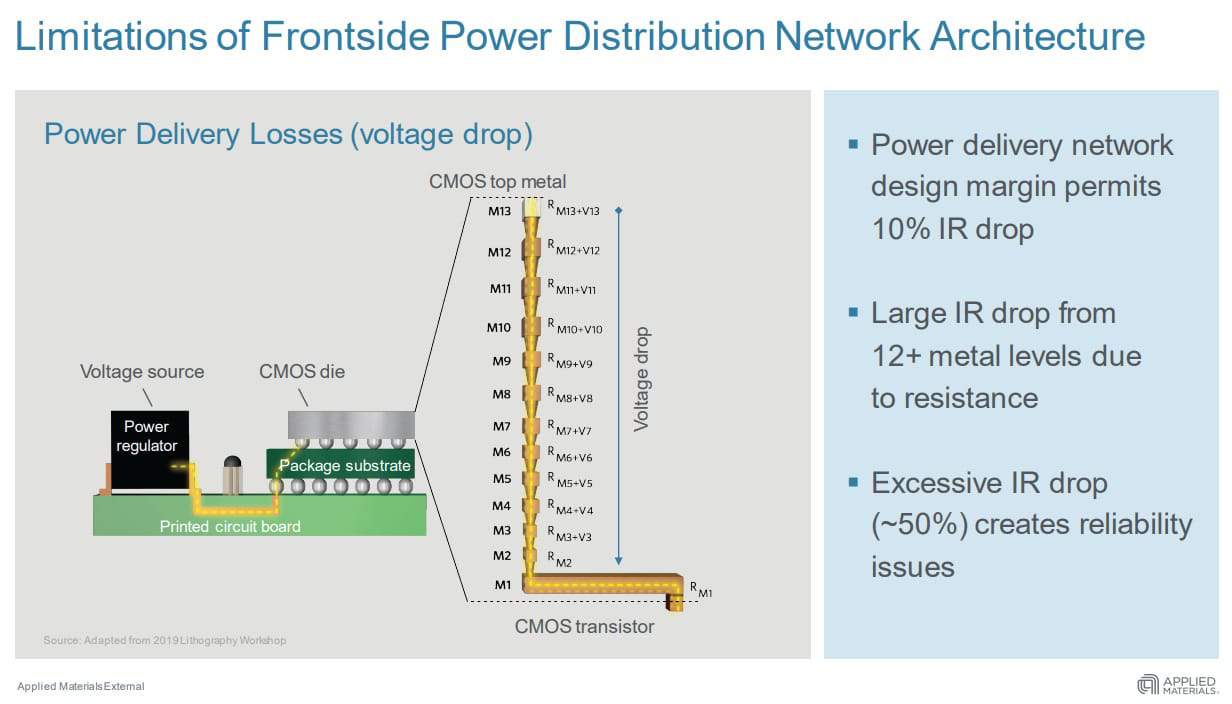

パッケージ内の電気を移動させることは、半導体の総合的な性能と電力に影響するため、エネルギーの観点から最も重要なことの1つだ。だが、半導体のマイクロレベルでの抵抗の課題を超えて、一般的な半導体の配電層では、複雑さの限界に達している。一般的な半導体は、ウェハーの表側で何層にも積み重ねられており、長い間、この方法でスケーリングしてきたが、何層もの金属配電網があり、今やIR(抵抗)ドロップが累積して手に負えなくなり始めているのだ。

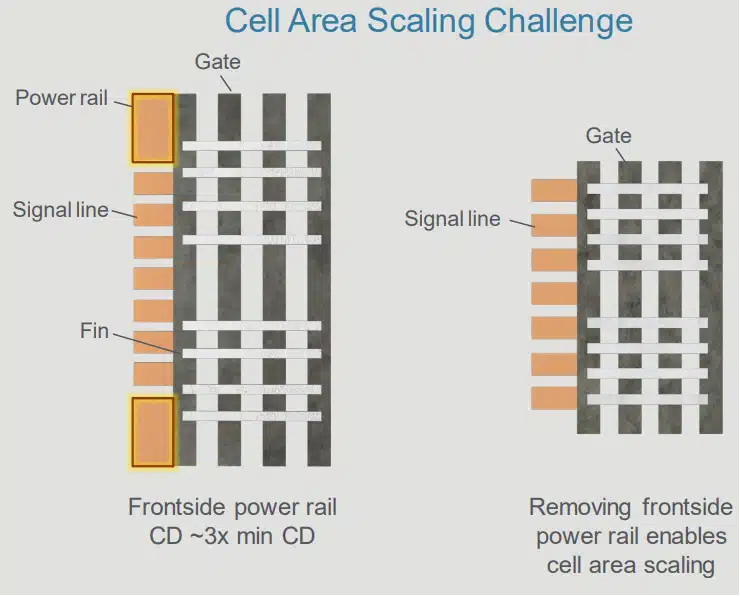

特に、「パワーインターコネクト」は複雑な BEOLネットワークの中でますますスペースを奪い合い、配線リソースの少なくとも 20%を占めるようになっている。また、スタンダードセルレベルでは、電源とグランドレールがかなり大きな面積を占めており、スタンダードセルのさらなる高さ方向のスケーリングに制限を与えている。システムレベルでは、電力密度とIRドロップが劇的に増加し、設計者は電圧レギュレータとトランジスタ間の電力損失に対して許容される 10%のマージンを維持することが要求される。

連続した層は電圧降下を引き起こし、より小さな層では高い抵抗がこれを補う。半導体の背景となるこれらの層は、最も重要な層である実際のトランジスタそのものをトータルに設計するために必要不可欠なものなのだ。だが、表側でこのような大規模な積層はできない。では、どうすればいいのか?そこで登場するのが、バックサイド・パワーデリバリー・ネットワーク(BSPDN)というわけだ。これは信号層と電源層を分割するもので、半導体構造の内部を再編成する巧妙な手法である。

BSPDNの枠組み

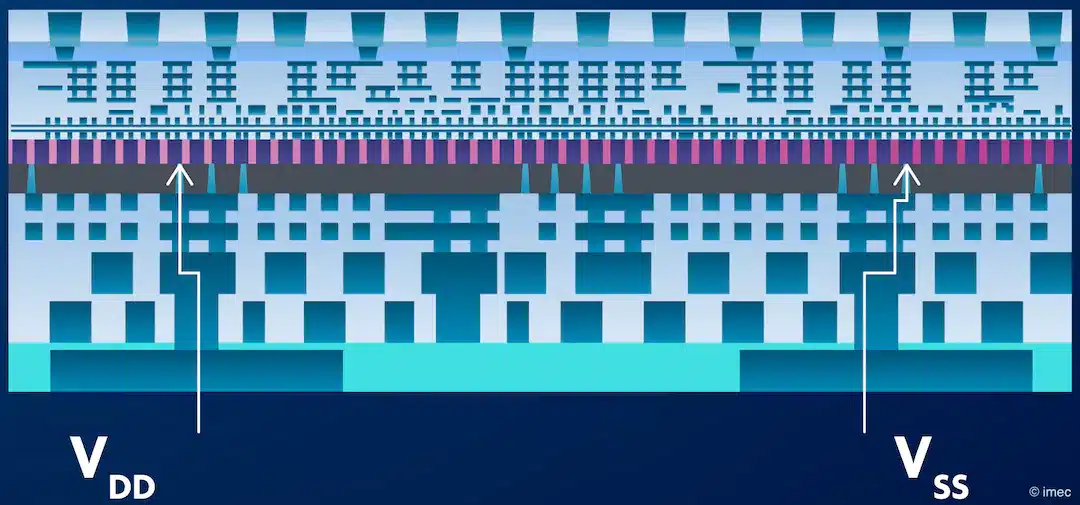

これまで配電網と信号網を同じ面で行っていたところ、配電網全体をシリコンウェハーの裏面に移動させることで、より多くのトランジスタのためのスペースが確保できるようになるというのは、至極簡単な道理だろう。

これにより、電子が複雑なBEOLスタックを通過することなく、抵抗の少ない幅の広い金属線を通してスタンダードセルに直接電力を供給することが可能になる。このアプローチは、IRドロップを改善し、電力供給性能を向上させ、BEOL内の配線混雑を緩和し、適切に設計されればスタンダードセルの高さをさらに拡張できることが期待出来るのだ。

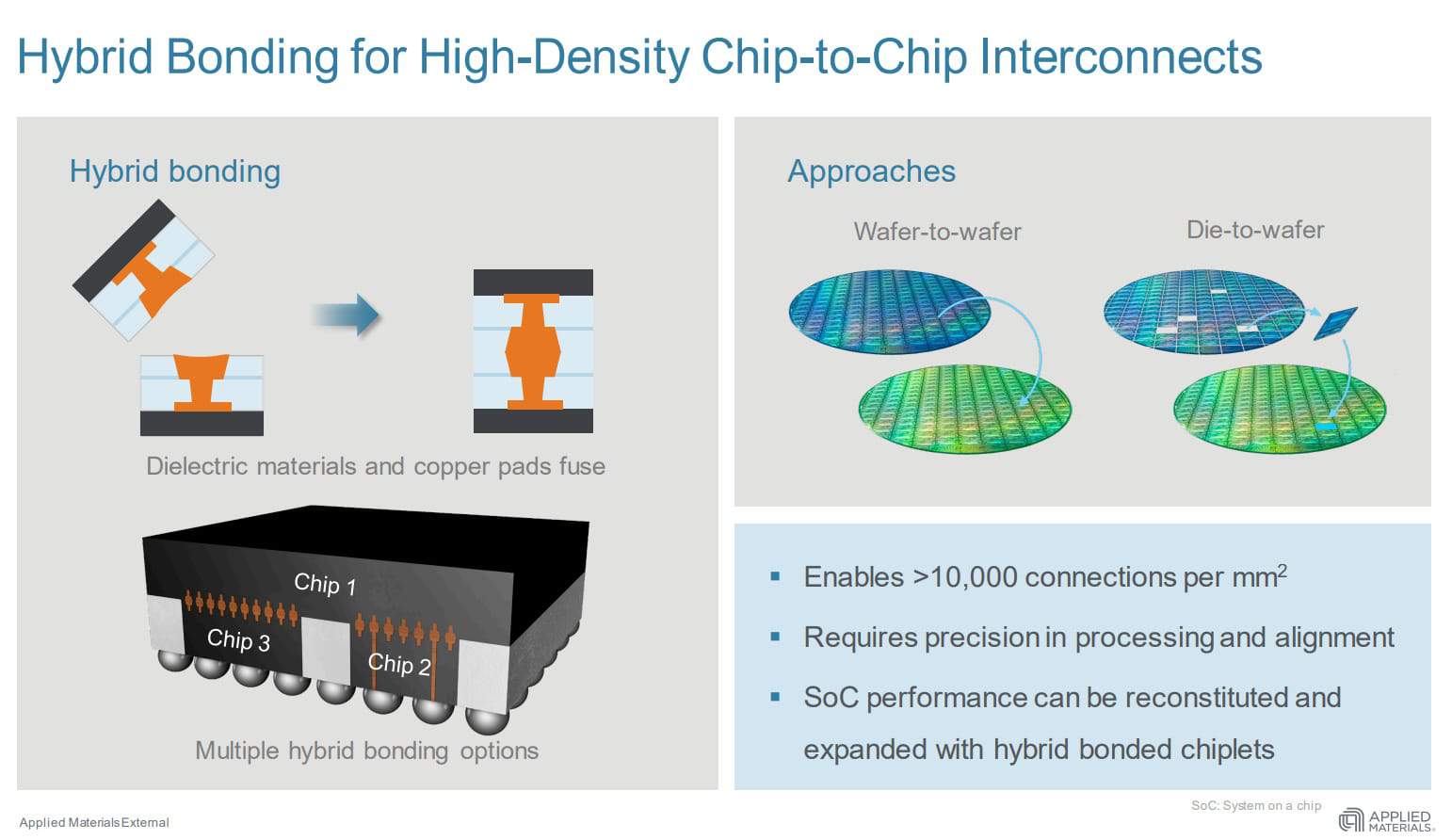

この新しい技術はこれまでになかったものだが、先進的なパッケージングのトレンドの延長線上にあるものだ。従来は半導体の片面だけを作っていたが、今はハイブリッド接合(ハイブリッドボンディング/ Hybrid Bonding)でチップ同士を接合するようになっている。エンジニアは、パワー層をチップの下側に接着することで、スペースを節約し、抵抗の問題を解決できることに気づいたのだ。

BSPDNでは、パワーレールがロジックセルの外側に移動するため、ロジック密度が向上する。Applied Materialsは、これは2世代分のリソグラフィースケーリングに相当すると推定している。電力はトランジスタの直下から供給されるため、IRドロップは大幅に低減されるのだ。

Armとimecが行ったシミュレーションと製造に関する研究では、Nano TSVを2μmより近くに配置できれば、バックサイドの電力供給はフロントサイドの電力供給ネットワークの7倍の効率になることが判明しているとのことだ。

以下に、Applied MaterialsによるPlanarからFinFET、GAA、そして最終的にBSPDNを備えたGAAの移行によるスケーリング効果の予測を掲載する。GAAまではリソグラフィの進化による物だったが、BSPDNは先進的なパッケージングにより達成される縮小となる点が、これまでと異なる。

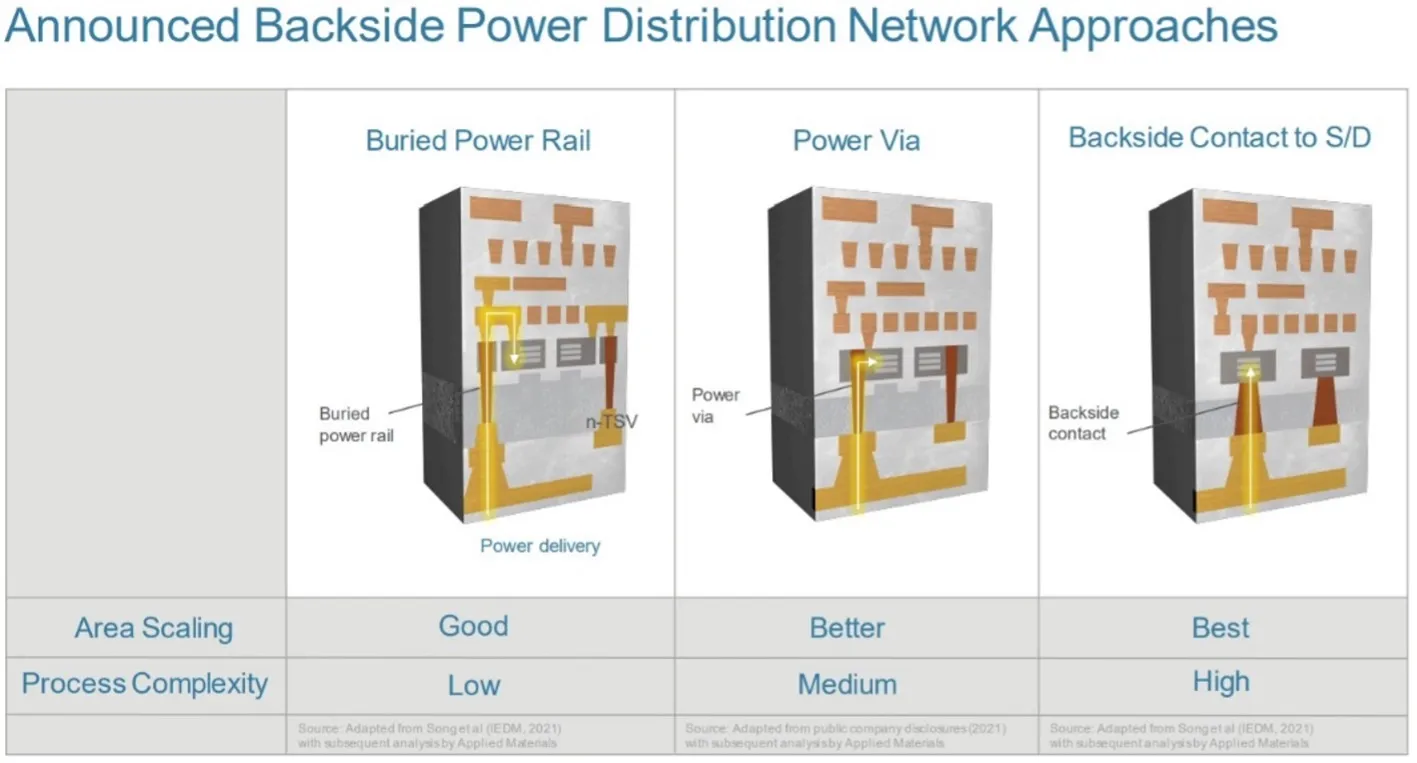

BSPDNのアプローチは非常に新しく、Buried Power Rails、PowerVia、Backside Contact to Source/Drainと言った様々なアーキテクチャがあるが、それぞれ以下にまとめられているように長所・短所がある。

そもそも、理想的な電力供給ネットワーク(PDN)は、どのような活動中でもIC上のアクティブな回路に一定かつ安定した供給電圧を供給してくれるようなものを指す。ここで重要となるパラメータは、ICの電源ピンから回路のトランジスタまで、すべてのインターコネクトパスにおけるPDNのDC抵抗である。

Applied MaterialsのマネージングディレクターであるMehul Naik氏がそれぞれの実装について説明してくれている:

「最初のアプローチ(Buried Power Rail)では、ロジックセルがパワーレールを保持し、裏面電力供給ネットワークはNano TSV(Through Silicon Via)でパワーレールに接続されています。2つ目のアプローチ(PowerVia)では、ロジックセルにパワーレールが存在しません。代わりにPowerViaでは裏面ネットワークからセルまたはトランジスタの接点に直接電力を転送します。この方法はより複雑ですが、電力効率が向上し、セル面積のスケーリングが可能になります。3番目のアプローチ(Backside Contact to S/D)では、バックサイド・ネットワークからの電力が各トランジスタのソースとドレインに直接接続されます」。

Buried Power Rail

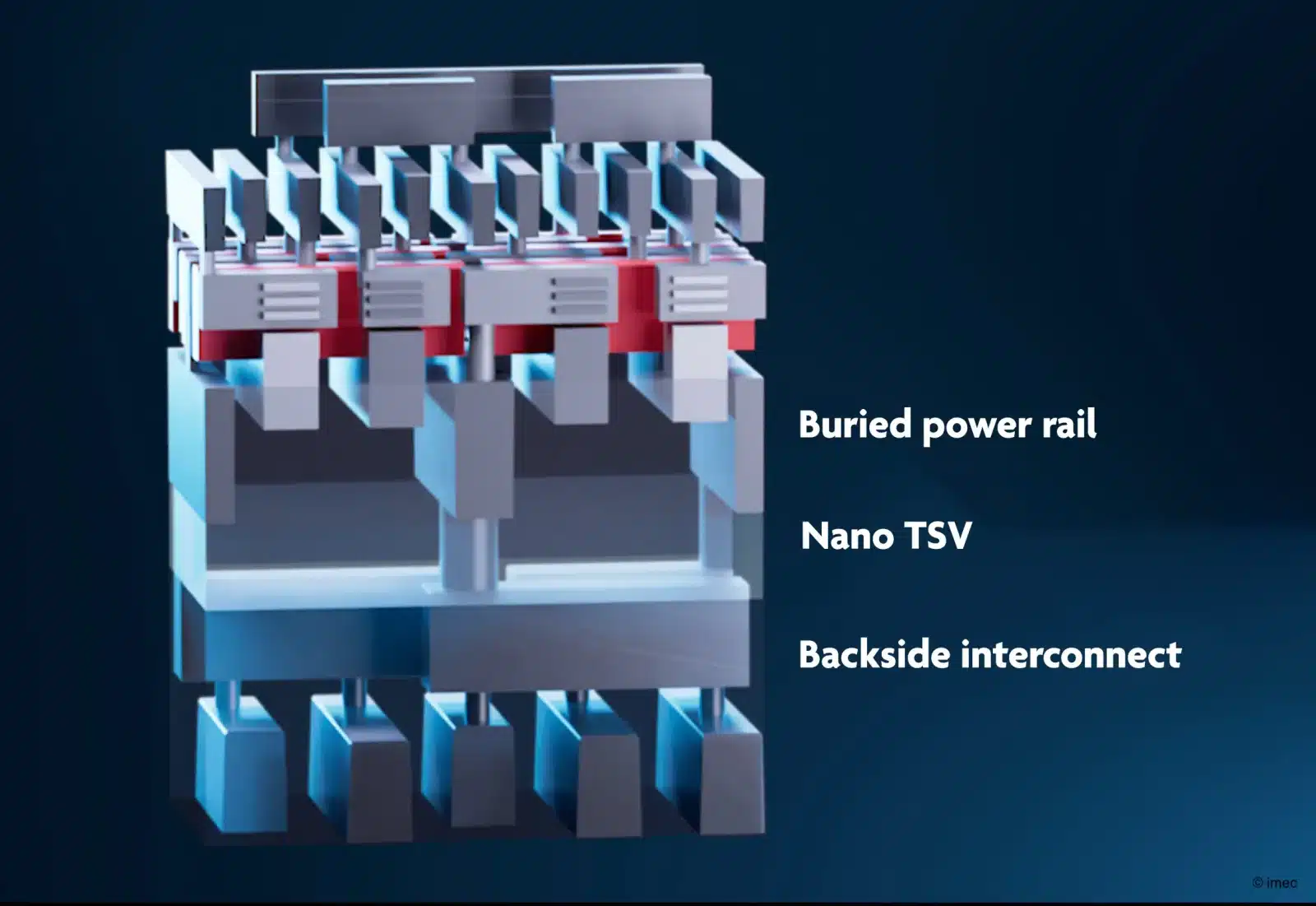

最初のBuried Power RailはImecが開発した物だ。Imecは裏面への電力供給アプローチを最初に開発した企業の1つである。

BPR はトランジスタの下に埋設される金属線構造で、一部は Si 基板内に、一部は浅いトレンチ絶縁酸化物内に埋設される。これは、従来スタンダードセルレベルでBEOLに実装されていたVDDとVSSのパワーレールの役割を担っている。このようにBEOLからFEOLへの歴史的な移行により、MINTトラックの数を減らすことができ、スタンダードセルのさらなる縮小が可能になる。また、スタンダードセルに対して垂直に設計することで、レールの大きさを緩和することができ、IRドロップをさらに低減させることができるのだ。

「BSPDNと、Buried Power Rail(BPR)には、ソース/ドレイン領域から、M0からBPRへのViaがあります。TSVがシリコンを貫通し、BPRに着地するわけですが、BPRはトランジスタが作られる前に作られるものです。TSV は、ゲート形成前、ソース/ドレインエピ形成前のナノシートフィンの間に位置します。これが、銅が使われない理由の1つです。タングステンやモリブデン、あるいはルテニウムのような、互換性のあるものでなければなりません」と、IMEC のシニアフェロー、研究開発担当副社長、3D システムインテグレーションプログラムのディレクターである Eric Beyne 氏は説明する。

BPRは、薄化されたウェハー裏面に加工された高アスペクト比のViaである Nano TSV と組み合わせることで、そのポテンシャルを十分に発揮することができる。これにより、ウェーハ裏面からフロントエンドのアクティブデバイスに最も効率よく電力を供給することができ、IRドロップ低減の面で最大の効果を得ることができるのだ。

これらを製造フローに組み込むこと自体、大変なことだ。「ゲートオールアラウンドと金属を蒸着すると、フィンが厚くなり、隣り合うフィンの間隔が非常に狭くなるからです。そのため、さらに小さなフィーチャーサイズで、ビアを深くしなければならないのです。」とBeyne氏は説明する。

また、「裏面パワーレールへの短いViaは、BPRに沿った狭いスペースに配置することができ、良好な性能上の利点をもたらす」とも指摘している。

BPRは、フィン方向と平行に走り、一部は浅いトレンチの絶縁体に、一部はシリコン基板に埋設される。これが、M0やM1にパワーレールを持つ従来のパワーグリッドとは異なり、標準的なセルの高さ低減を可能にするのだ。TSMCはこのBuried Power Railを採用する予定である。

PowerVia

PowerViaについては、その名称を聞いたことがあるかも知れない。これは、Intelが2024年頃に、20A(オングストローム)ノードにおいて、RibbonFET(GAAFET)と共に導入する予定のバックサイドパワーデリバリー方式である。

電源配線は、トランジスタ層の下、ウェハーの裏側に配置されてる。低抵抗(低損失)、良好な接地(パワーインテグリティの確保)のために最大限の金属体積を確保するなど、電力供給用に最適化された金属層のネットワークを通じて、パッケージからトランジスタに直接電力が供給される。同様に、信号層(上部)では、信号トレースの分離、トレースの短縮、曲がりやコーナーの減少、誘電体材料の使用などのためにスペースが確保されており、信号配線が最適化されて信号干渉、電力損失、カップリング効果を大幅に低減している。

信号と電力は、ナノTSVを使ってトランジスタ層に接続される。このTSVは、現在の最先端ICパッケージで使用されているTSVの500分の1の大きさである。このPowerViaは前述の通り、Buried Power Railよりも複雑な技術となる。

PowerVia はまだ実装されていないテクノロジだが、Buried Power Rail は現在のツールで実行できることを考えると、TSMC が失敗することはないだろう。そのため、TSMC は典型的な方法で、保守的だが達成可能なアーキテクチャの選択を実行するが、Intelは新たな技術の開拓によって、よりTSMCよりも積極的に性能向上を求めていくようだ。

「IntelのPowerViaは、裏面電力供給ネットワークと従来のソースコンタクトをよりダイレクトに単一機能で接続し、imecのアプローチと比較してはるかに低い抵抗値を達成できると考えています」とIntel のロジック テクノロジー開発担当シニア バイス プレジデント兼共同ゼネラル マネージャーである Sanjay Natarajan氏は述べている。

BSPDNを実現するための長い道のり

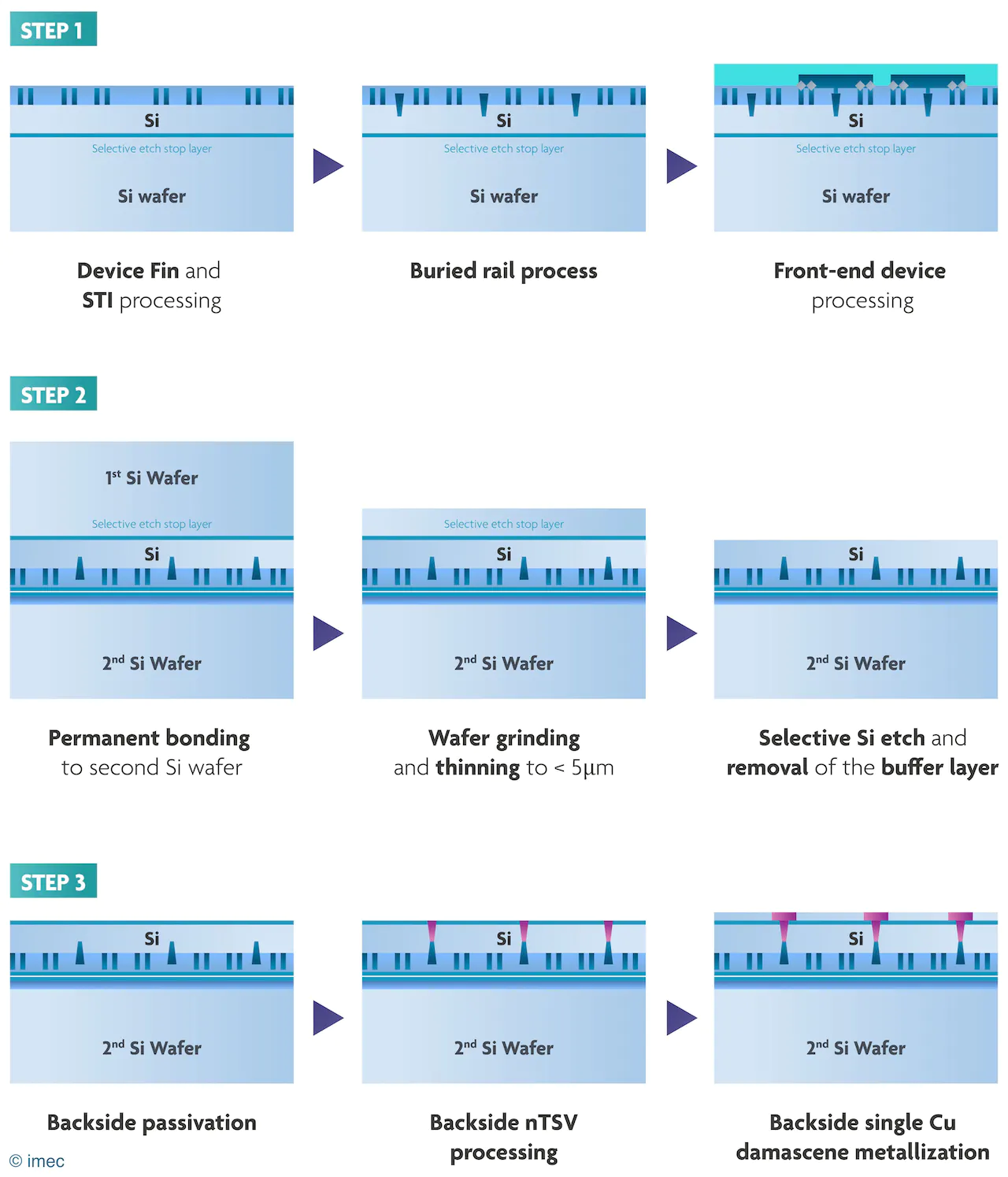

しかし、BSPDNを製造工場で実現するためには、いくつかのプロセスや材料の変更が必要となる。以下では、BSPDNの1つBuried Rail Processの実装を作成するためのプロセスフローを掲載する。この実装では、非常に薄いウェハー裏面で処理されたNano TSVがBPRの上に配置される。デバイス、例えばウェハーの前面で処理されたスケーリングされた FinFET は、BPR と Nano TSV を介してウェハーの裏面に接続される。

重要なのは、現在すべてのウェハーファブで行われているように、トランジスタを先に処理すれば、新しい配線金属を2nmノードで必ずしも採用する必要がないということだ。実際、IntelのPowerViaは、まさにそれを可能にしているようだ。「PowerViaの性能を最大限に引き出すために、(タングステンを含む)従来のフロントエンドのコンタクトメタルと先進的なメタルプロセスの両方に対応できるようにPowerViaプロセスを設計しました」とNatarajan氏は言う。

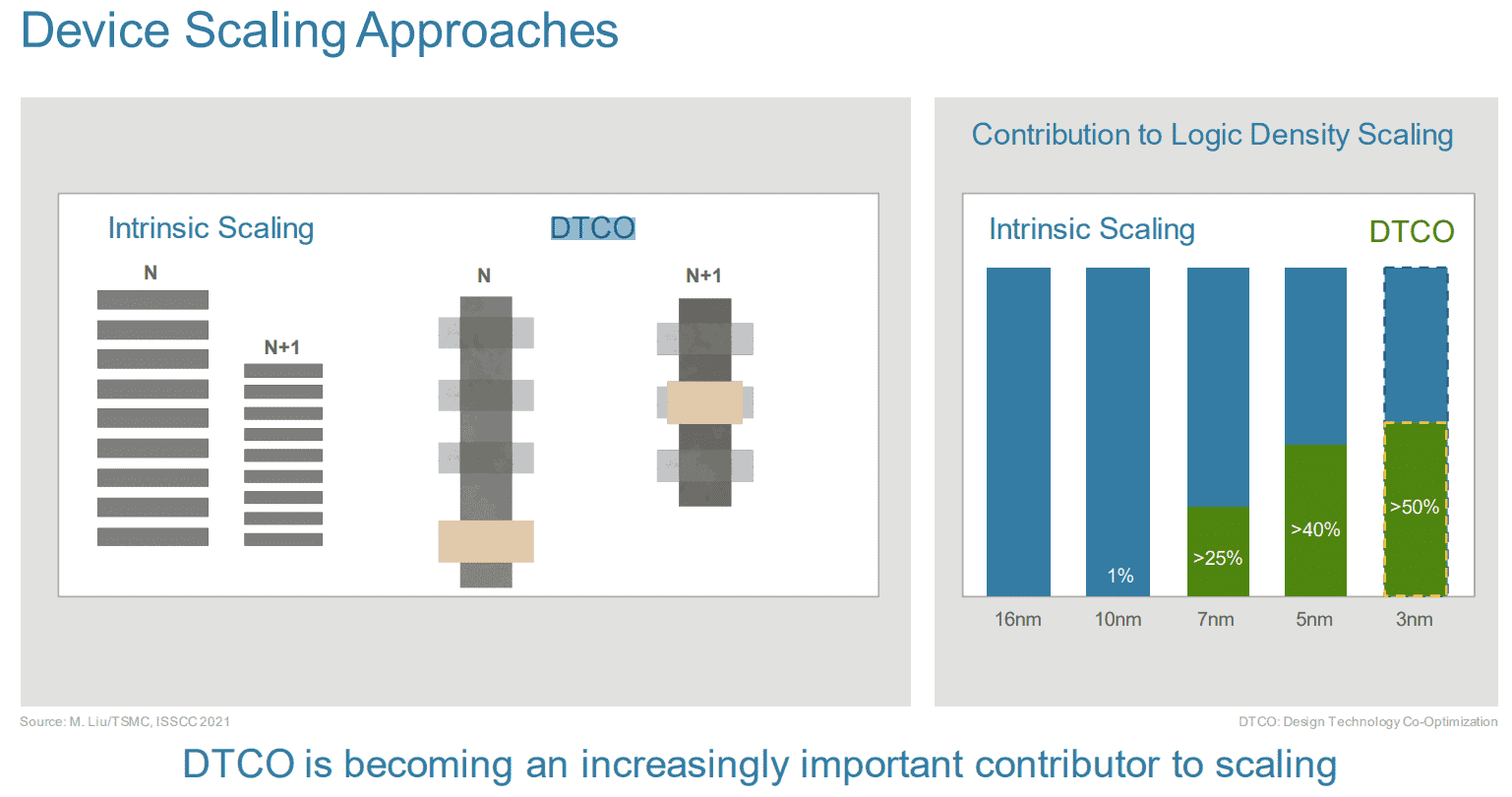

BSPDNによる変革は、設計にも大きな変革をもたらす。この方法論全体には、Design Technology Co-Optimization(DTCO)という新しい名前もついている。DTCOは、なぜ製造コストが高くなっているのかを示す好例であり、こうした技術的なチャレンジが、今後のスケーリングの方法となるのだ。次のグラフは、DTCOが密度スケーリングにつながる割合を示している。

DTCOは、巧妙な変更から、半導体をスケールアップするデファクトの方法へと移行することだろう。これは、チップをより高価で複雑にするコストと設計の増分に繋がるが、半導体の製造にステップとプロセスを大幅に追加してくれる。もちろん、その複雑さはセミキャパに適している。

Applied MaterialsのマネージングディレクターMehul Naik 氏は、バックサイドパワーデリバリーを、設計とプロセスの革新がシステムレベルの利益をもたらすDTCOの一形態であると説明した。また、バックサイドナノTSVを構築する際に存在する熱的な制約を強調している。

「我々は、トランジスタソースへの裏面コンタクトの抵抗をできるだけ小さくする必要があります。このためには、通常、高温のエピとアニール工程が必要です。しかし、裏面コンタクトは表側のトランジスタや配線がある状態で製造されるため、この高温で劣化してしまいます。そこでApplied Materialsでは、プリクリーン、選択的シリサイド膜、ALDまたはPVDライナー膜、新しいメタルフィル用のチャンバーなど、最大7工程を高真空で行う低温ソリューションを開発中です。共同最適化されたCMP工程により、裏面コンタクト層は完全に均一化され、その上に銅の裏面配電網を構築することができるのです。」

また、BSPDNを実現するためには、フィルム、エッチング、リソグラフィ、ウェットだけでなく、ウェハー接合や薄膜化技術など、プロセスやツールの継続的な進化が必要だ。

どのようにスケーリングを改善するかの具体的なメカニズムは、マイクロレベルでの高度なパッケージングの一形態であり、それは、2つのチップを1つのダイに反転するハイブリッド接合(Hybrid Bonding)によるウェハー間の接合によるものだ。BSPDNは、スケーリングプロセスにおける最初の例に過ぎない。ここでの新技術は、ハイブリッド接合だ。下図は、左が古いインターコネクト方式、右が新しいインターコネクト方式を示す。

右の図を見ると、黒とグレーの金属層が見えるが、これがハイブリッド接合層で、2つのダイを合体させて裏面ネットワークを作り、信号とトランジスタのレベルを分離させるものだ。抵抗の問題を解決するだけでなく、セルサイズも20~30%小さくすることが出来るという。

さらに驚くべきは、BPRがPowerViaにスケールアップし、さらにBackside Contact Source/Drainにスケールアップするというロードマップが存在することだ。ハイブリッド接合は大きな意味を持ち、この効果により、シリコンが増え、工程が増え、全く新しい、非常に重要なツールが必要になる。Wafer-to-Wafer、Die-to-Waferのツールは非常に重要だ。

Applied MaterialsもBESIと共同でDie-to-Waferツールを提供するなど、多くの企業がこれを追求している。また、東京エレクトロンが提供する新しいツールであるWafer-to-Waferも忘れてはならない。これらの市場は実質的な増分成長ドライバーであり、配線の機会はWFEの3倍の速度で成長すると予想される。このトレンドに最も影響を受けているセミキャップ企業を見つけることは、セミキャップの相対的なファンダメンタルズ・アウトパフォーマンスにとってかなりのアドバンテージになる。より良い面積効率と性能向上のために、バックサイドパワーデリバリーネットワーク(BSPDN)は魅力的な選択肢である。

2大ファブの運命は、リソグラフィーの決定ではなく、高度なパッケージングの決定にかかっており、おそらく、BSPDNタイプの決定だけでなく、別の高度なパッケージングの決定が推進役となるであろう。

Sources

- Applied Materials: New Ways to Wire and Intergrate Chips (PDF)

- imec: How to power chips from the backside

- IEEE Spectrum: NEXT-GEN CHIPS WILL BE POWERED FROM BELOW

- Semiconductor Engineering: Challenges In Backside Power Delivery

コメントを残す